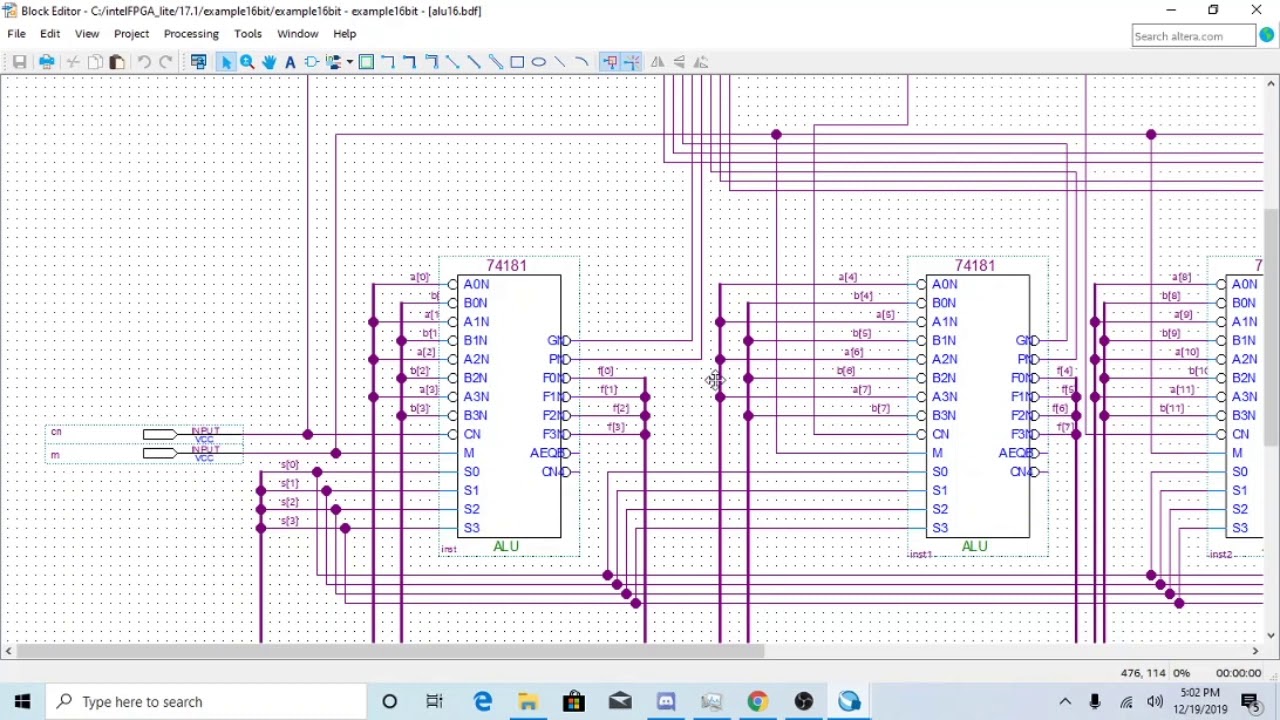

16-bit Alu

Digital logic Alu bit vhdl Alu bit 16 logisim using sub add

16-bit breadboard ALU : r/beneater

Alu bit diagram 16 code vhdl structural components alus creating architecture declare which stack Xor inputs sum outputs Alu logic circuits schematic wellesley operation herbology assignments cs240

Alu bit

Breadboard alu 16 bit comments 16bit16-bit breadboard alu : r/beneater Logisim adder subtractor multiplier implement solveSolved 1. design a 1-bit alu. below is a block diagram of a.

Bit less thanCs 240: circuit herbology 16 bit alu tutorial with 74181 & 74182Functional block diagram of one bit alu.

Dupincomp: 4-bit alu

16-bit aluAlu in detail 16 bit aluBuilding an arithmetic logic unit (alu) using hdl part 1.

Alu bit 16Logic arithmetic hdl Alu bit diagram block carry below let solved simplified give transcribed text show problem been hasAlu functional.

Alu bit table truth

16-bit alu design in vhdl16 bit alu using logisim(and,or,add,sub) You must give the 1 bit alu and the 64 bit alu.

.

16 Bit ALU using logisim(AND,OR,Add,Sub) - YouTube

16-bit breadboard ALU : r/beneater

16 Bit ALU Tutorial with 74181 & 74182 - YouTube

Solved 1. Design a 1-bit ALU. Below is a block diagram of a | Chegg.com

Building an Arithmetic Logic Unit (ALU) using HDL Part 1 | by Aditya

DupinComp: 4-bit ALU - Design

Functional block diagram of one bit ALU | Download Scientific Diagram

ALU in Detail - Tutorials

16-bit ALU Design in VHDL - FPGA4student.com